# (12) United States Patent

Yamazaki et al.

### US 6,828,951 B2 (10) Patent No.:

Dec. 7, 2004 (45) Date of Patent:

## (54) SEMICONDUCTOR DISPLAY DEVICE

(75) Inventors: Shunpei Yamazaki, Tokyo (JP); Jun

Koyama, Kanagawa (JP)

Assignee: Semiconductor Energy Laboratory

Co., Ltd., Atsugi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 10/195,521

Jul. 16, 2002 (22)Filed:

(65)**Prior Publication Data**

US 2002/0180672 A1 Dec. 5, 2002

## Related U.S. Application Data

Division of application No. 09/753,708, filed on Jan. 4, 2001, now Pat. No. 6,424,326.

#### Foreign Application Priority Data (30)

| Jan. | 11, 2000 (JP)         |            |            | 2000-002042          |

|------|-----------------------|------------|------------|----------------------|

| (51) | Int. Cl. <sup>7</sup> |            |            | G09G 3/30            |

| (52) | U.S. Cl               |            | 345        | / <b>77</b> ; 345/76 |

| (58) | Field of Searc        | <b>h</b> 3 | 45/77, 76; | 315/169.1;           |

#### (56)References Cited

## U.S. PATENT DOCUMENTS

| 5,247,190 A | 9/1993 | Friend et al. | 257/40 |

|-------------|--------|---------------|--------|

| 5,399,502 A | 3/1995 | Friend et al. | 438/22 |

| 5,597,223 A  | *   | 1/1997  | Watanabe et al 353/97 |

|--------------|-----|---------|-----------------------|

| 5,745,085 A  |     | 4/1998  | Tomio et al 345/63    |

| 5,886,474 A  |     | 3/1999  | Asai et al            |

| 6,069,676 A  |     | 5/2000  | Yuyama 349/62         |

| 6,072,448 A  | *   | 6/2000  | Kojima et al 345/63   |

| 6,320,325 B1 |     | 11/2001 | Cok et al.            |

| 6,356,029 B1 | *   | 3/2002  | Hunter 315/169.1      |

| 6,392,617 B1 | *   | 5/2002  | Gleason               |

| 6,404,137 B1 |     | 6/2002  | Shodo                 |

| 6,411,306 B1 | . * | 6/2002  | Miller et al 345/690  |

| 6,496,218 B2 | *   | 12/2002 | Takigawa et al 348/42 |

| 6,518,962 B2 | *   | 2/2003  | Kimura et al 345/211  |

## FOREIGN PATENT DOCUMENTS

| JP | 10-092576   | 4/1998  |

|----|-------------|---------|

| WO | WO 90/13148 | 11/1990 |

### OTHER PUBLICATIONS

Schenk et al.; "Polymers for Light Emitting Diodes"; Euro-Display '99 Proceedings; pp. 33-37; Sep. 6-9, 1999.

\* cited by examiner

Primary Examiner—David Nelms Assistant Examiner—Tu-Tu Ho

(74) Attorney, Agent, or Firm-Fish & Richardson P.C.

#### (57)**ABSTRACT**

To provide a semiconductor display device capable of displaying an image having clarity and a desired color, even when the speed of deterioration of an EL layer is influenced by its environment. Display pixels and sensor pixels of an EL display each have an EL element, and the sensor pixels each have a diode. The luminance of the EL elements of each in the display pixels is controlled in accordance with the amount of electric current flowing in each of the diodes.

## 20 Claims, 25 Drawing Sheets

349/69

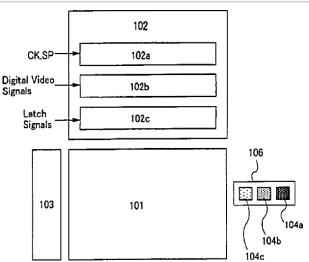

Fig. 1

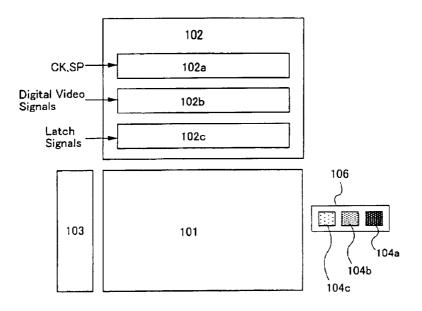

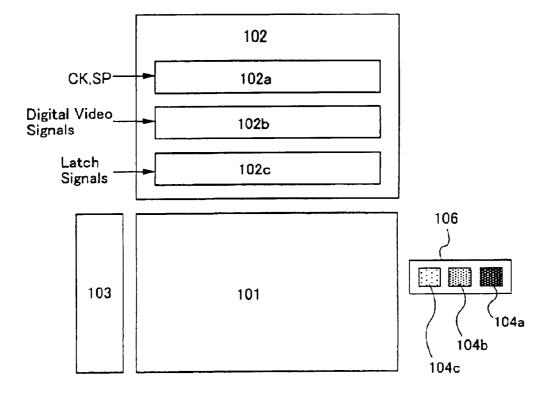

Fig. 3

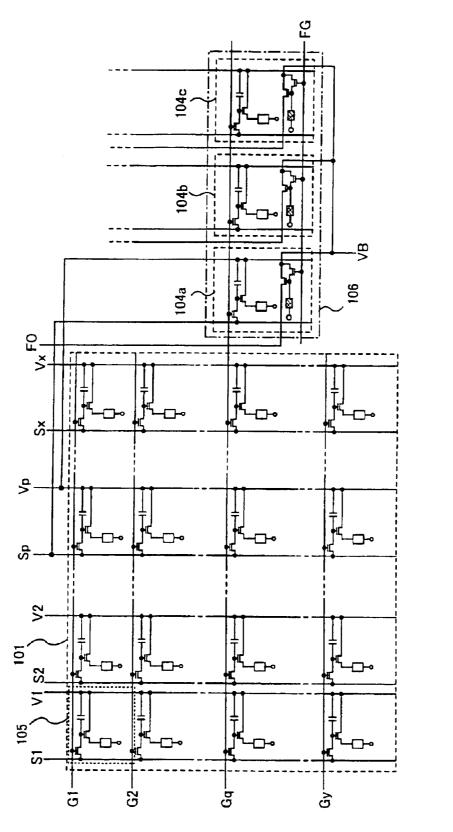

Fig. 4

Fig. 5

Fig. 6

Fig. 7

$\infty$

Fig. 15

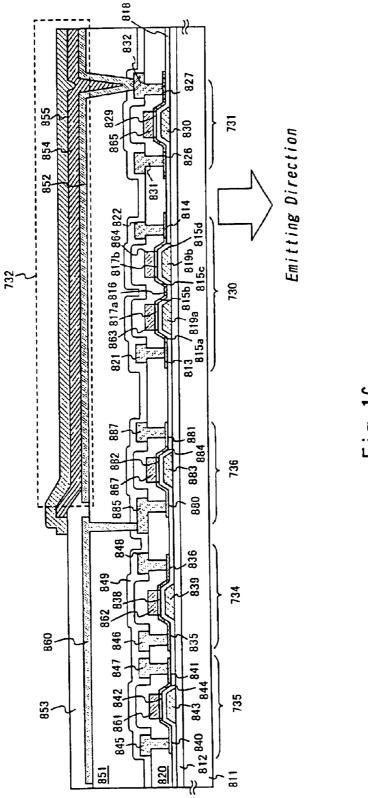

Fig. 16

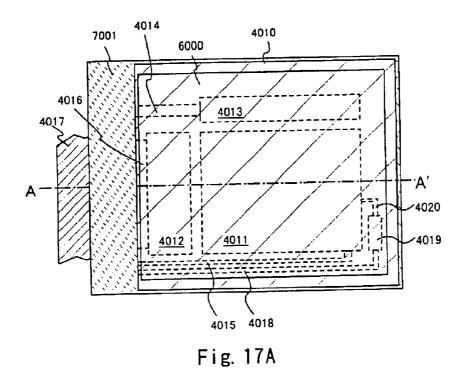

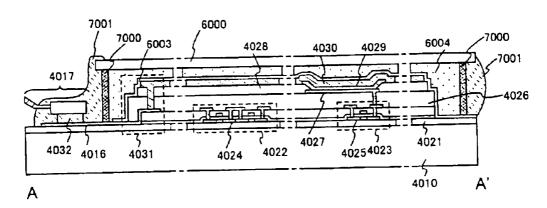

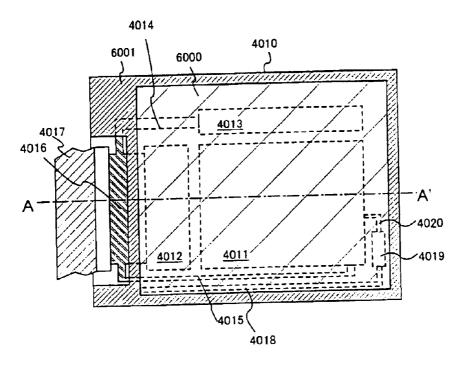

Fig. 17B

Fig. 18A

Fig. 20A

F18. 21

Dec. 7, 2004

## SEMICONDUCTOR DISPLAY DEVICE

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a divisional of U.S. Ser. No. 09/753, 708, filed Jan. 4, 2001 now U.S. Pat. No. 6,424,326.

### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to an EL display that is formed by fabricating an EL (Electro Luminescence) element on a substrate. Particularly, the present invention relates to an active matrix type EL display that uses a semiconductor element (an element employing a semiconductor thin film), and furthermore to a semiconductor display device employing the EL display.

### 2. Description of the Related Art

In recent years, technology for forming a TFT on a substrate has been largely improved, and an application <sup>20</sup> development of the TFT to an active matrix type semiconductor display device has been carried out. In particular, the TFT using a polysilicon film has a higher electric field effect mobility than the TFT using a conventional amorphous silicon film, and therefore, the TFT may be operated at a <sup>25</sup> high speed. Thus, the pixel control which has been conducted at a driver circuit outside of the substrate may be conducted at the driver circuit which is formed on the same substrate as the pixel.

Such an active matrix type semiconductor display device can, by preparing various circuits and elements on the same substrate, obtain various advantages such as a decrease in manufacturing cost, a decrease in the size of the semiconductor display device, an increase in yield, and a decrease in throughput.

Further, research on the active matrix type EL display having an EL element as a self-light-emitting element is becoming more and more active. The EL display is referred to as a light-emitting display, an organic EL display (OELD) or an organic light-emitting diode (OLED).

The EL display is a self-light-emitting type unlike a liquid crystal display device. The EL element is constituted such that a layer containing an organic compound (hereinafter, referred to as an EL layer) is sandwiched between a pair of electrodes (anode and cathode). However, the EL layer normally has a lamination structure. Typically, the lamination structure of a "hole transport layer/a light emitting layer/an electron transport layer" proposed by Tang et al. of the Eastman Kodak Company can be cited. This structure has a very high light-emitting efficiency, and this structure is adopted in almost all the EL displays which are currently subjected to research and development.

When the EL element obtains Luminescence (Electro Luminescence) which is generated by applying a voltage to 55 the EL element, it is composed of an anode layer, an EL layer, and a cathode layer. There are two types of luminescence in an organic compound, one being a luminescence that is generated when the organic compound returns from a singlet excitation state to a ground state (fluorescence) and the other being a luminescence that is generated when the organic compound returns from a triplet excitation state to a ground state (phosphorescence). Either type of luminescence may be used in the EL display of the present invention.

In addition, the structure may be such that on the electrodes, a hole injection layer/a hole transport layer/a

2

light emitting layer/an electron transport layer, or a hole injection layer/a hole transport layer/a light emitting layer/an electron transport layer/an electron injection layer may be laminated in order. Phosphorescent dye or the like may be doped into the light emitting layer.

In this specification, all the layer s provided between a pair of electrodes are generally referred to as EL layers. Consequently, the hole injection layer, the hole transport layer, the light emitting layer, the electron transport layer, the electron injection layer and the like are all included in the EL layers.

In this specification, a light emitting element, which is composed of an anode, an EL layer and a cathode, is referred to as an EL element.

The deterioration of the EL material of the EL layer has become a problem in the realization of the EL display, which leads to the reduction in the luminance of the EL element.

The EL material of the EL layer is inferior to moisture, oxygen, light, and heat, which are the factors that promote the deterioration of the EL layer. To be more specific, the rate at which the EL layer deteriorates is influenced by the structure of a device driving the EL display, characteristics of the EL material structuring the EL layer, materials of an electrode, conditions of the manufacturing processes, a driving method of the EL display and the like.

The EL layer deteriorates even if a constant voltage from a pair of electrodes is applied thereto, whereby the luminance of the EL element is reduced. Thus, an image displayed on the EL display is not clear because of the reduction in the luminance of the EL element.

Further, Color display systems of the EL display are roughly divided into four: a system where three kinds of EL elements corresponding to R (red), G (green), and B (blue), respectively, are formed; a system where EL elements emitting white light are combined with a color filter; a system where EL elements emitting blue or blue-green light are combined with a fluophor (fluorescent color conversion layer: CCM); and a system where EL elements corresponding to R, G, and B are superimposed on a transparent electrode used as a cathode (an opposing electrode) (RGB stacking method).

The EL material that structures the EL layer differs depending on the luminescing color of the EL layer. Therefore, in the color display system that employs three kinds of El elements corresponding to the colors R (red), G (green), and B (blue), the three kinds of EL elements of the EL layer corresponding to RGB each may deteriorate at different rates. In this case, the luminance of the EL elements that correspond to RGB becomes dissimilar, respectively, as time passes. Consequently, an image having a desirable color cannot be displayed on the EL display.

### SUMMARY OF THE INVENTION

The present invention has been made in view of the above, and therefore has an object to provide an EL display capable of performing a clear and desirable color display by suppressing a reduction in luminance of an EL element even if an EL layer is deteriorated.

The EL display of the present invention has a sensor portion for detecting a luminance of a portion for displaying an image of the EL display (display portion) and revising the luminance to a desirable value. The sensor portion includes one or a plurality of pixels. It is to be noted that the pixel(s) of the sensor portion will hereinafter be referred to as sensor pixel(s) throughout this specification.

The sensor pixel(s) is composed of an EL element and a light receiving diode that detects the amount of change in the luminance of the EL element. It is to be noted that throughout this specification, the EL element of the sensor pixel(s) will hereinafter be referred to as a sensor EL element.

The sensor EL element has the same structure as that of the EL element (hereinafter referred to as display EL element) of the pixel (hereinafter referred to as display pixel) of the display portion. At least a material that constructs a pair of electrodes and a material that constructs a 10 lamination structure of an EL layer and the EL layer are the same, respectively.

Then, a signal, which is the same as a signal inputted to an arbitrarily selected display EL element, is fed to the sensor EL element. In this specification, the input of a signal to the EL element (display EL element and sensor EL element) means that an electric potential of the signal is applied to one of the electrodes of the EL element, and an EL drive voltage is applied to the EL layer. Here, the EL drive voltage is the electric potential difference between the 20 electric potential of the signal applied to one of the electrodes of the EL element and the constant electric potential applied to the other electrode thereof.

Thus, an equivalent voltage is applied to the EL layers of the sensor EL element and the arbitrarily selected display EL element, whereby the deterioration rates of the EL layers are nearly equivalent. Therefore, the luminance of the sensor EL element and the luminance of the display EL element maintain almost equivalent states even as time elapses.

Light emitted by the sensor EL element, on one hand, is irradiated to the light receiving diode of the senor pixel. Then, the light receiving diode detects the luminance of the sensor EL element. On the basis of the information of the luminance of the sensor EL element that was detected, the luminance of the display EL element is revised, and the luminance of the sensor EL element is also revised at the same time.

By adopting the above structure, the present invention has made it possible for the EL display to perform a clear and 40 desirable color display by suppressing the reduction in luminance of the EL element even if the EL layer is deteriorated.

The EL display of the present invention may be of a color display system that employs a display EL element emitting 45 manufacturing an EL display of the present invention; white light, or a color display system that employs display EL elements corresponding to the colors RGB, respectively. In case of the color display system that employs the display EL elements corresponding to each of the colors RGB, it is preferable that the senor pixels corresponding to each of the 50 colors RGB are provided in the sensor portion. However, the present invention is not limited to the structure thereof. It may be a structure in which the sensor pixels, which correspond to either 1 or 2 colors of the RGB colors, are provided in the sensor portion. In particular, it is effective to 55 provide the sensor pixel that corresponds to the color of which the deterioration of the EL layer is remarkable in the sensor portion to thereby display an image having a desirable color.

It is further preferable that the display EL element and the 60 sensor EL element are formed at the same time under the same conditions. The deterioration rates of the EL layers of the display EL element and the sensor EL element can be made equivalent by adopting the above structure. Therefore, the luminance of the sensor EL element that will be detected 65 by the light receiving diode becomes equivalent with the luminance of the display EL element, to thereby detect the

change in the luminance of the display EL element more accurately. Thus, it becomes possible to revise the luminance of the display EL element to a desirable value.

Furthermore, when the sensor portion is formed simultaneously with the display portion on the substrate, as the manufacturing process of the El display, only the process of forming the light receiving diode has to be added to the manufacturing process in the case where the sensor portion is not provided. Therefore, there is no need to remarkably increase the number of manufacturing processes, thereby making it possible to suppress the number of manufacturing processes.

It is to be noted that a portion of the display portion may be used as the sensor portion. That is, among the pixels of the display portion, one or a plurality of pixels that are arbitrarily selected may be employed as sensor pixels and the rest of the pixels may be employed as display pixels. In this case, the size of the EL display can be suppressed because the space for the provision of the sensor portion can be omitted compared with the case of not including the sensor portion in the display portion.

### BRIEF DESCRIPTION OF THE DRAWINGS

In the accompanying drawings:

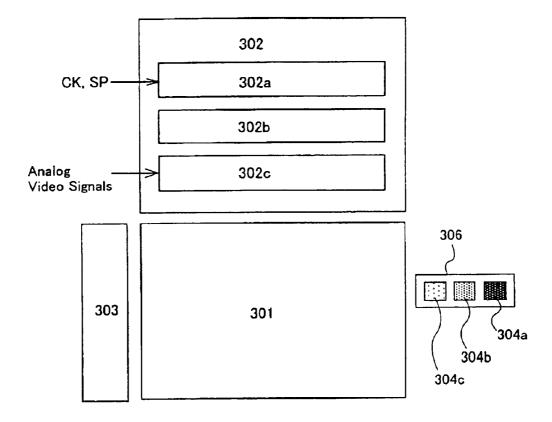

FIG. 1 is a schematic diagram of the top of an EL display of the present invention;

FIG. 2 is a circuit diagram of an EL display of the present invention:

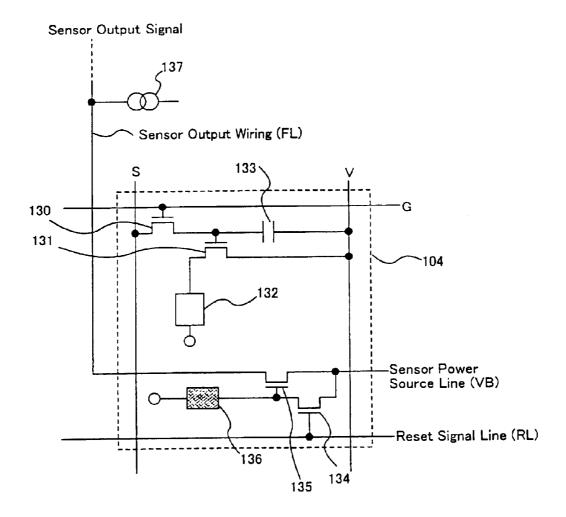

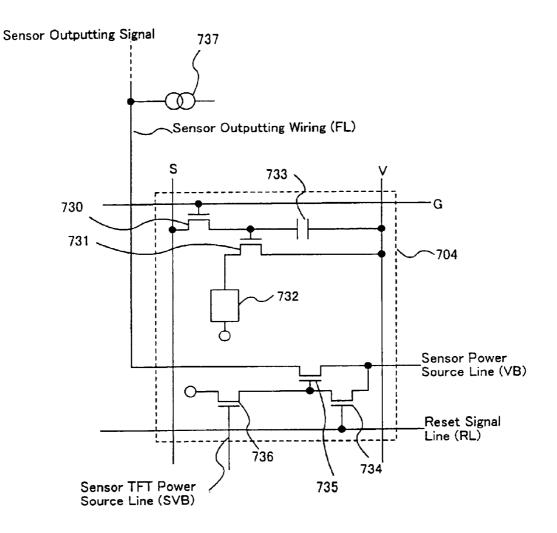

FIG. 3 is a circuit diagram of a sensor pixel of an EL display of the present invention;

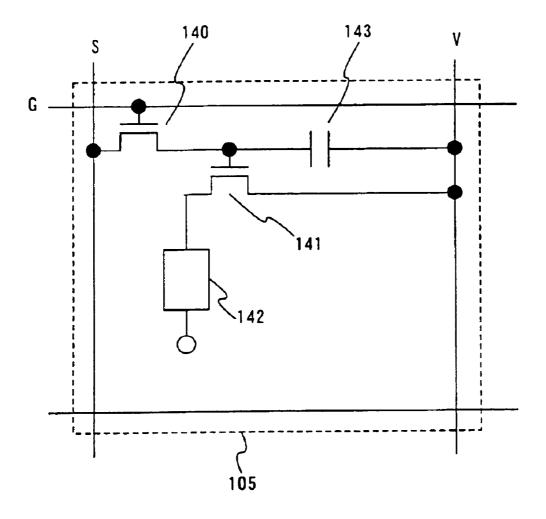

FIG. 4 is a circuit diagram of a display pixel of an EL display of the present invention;

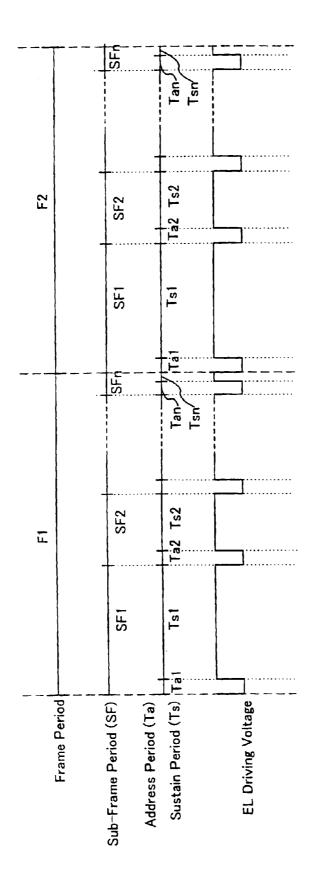

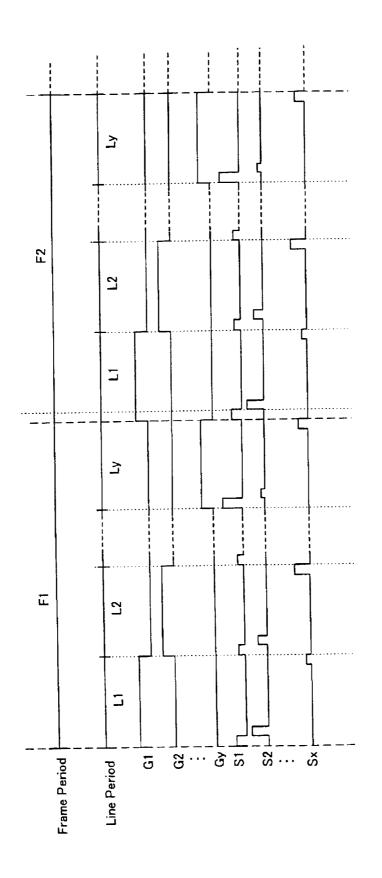

FIG. 5 is a timing chart when an EL display of the present invention is driven by a digital method;

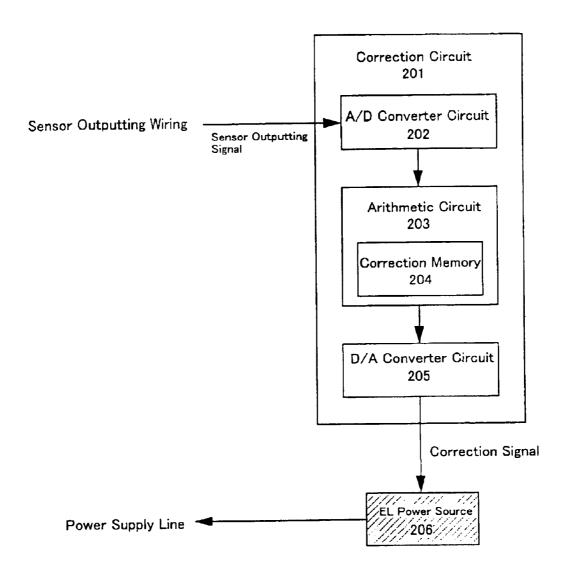

FIG. 6 is a block diagram of a correction circuit of an EL display of the present invention;

FIG. 7 is a schematic diagram of the top of an EL display of the present invention;

FIG. 8 is a timing chart when an EL display of the present invention is driven by an analog method;

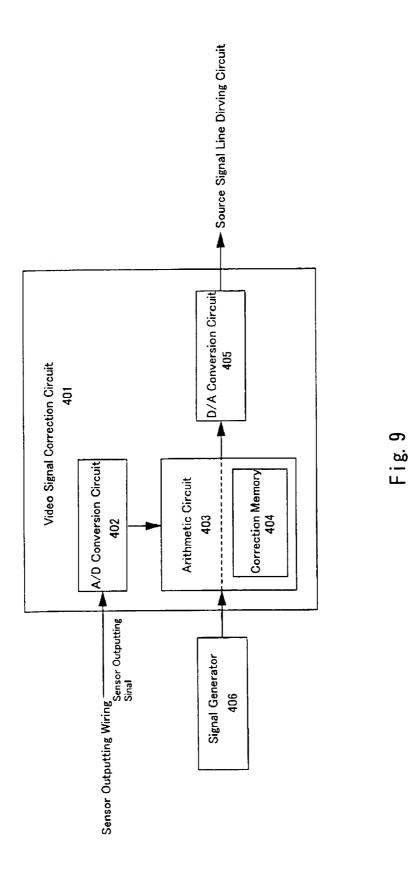

FIG. 9 is a block diagram of a video signal correction circuit of an EL display of the present invention;

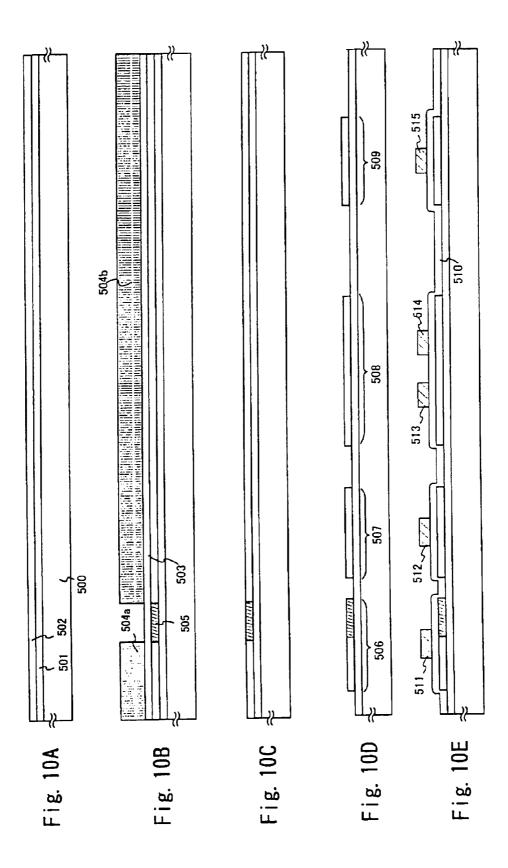

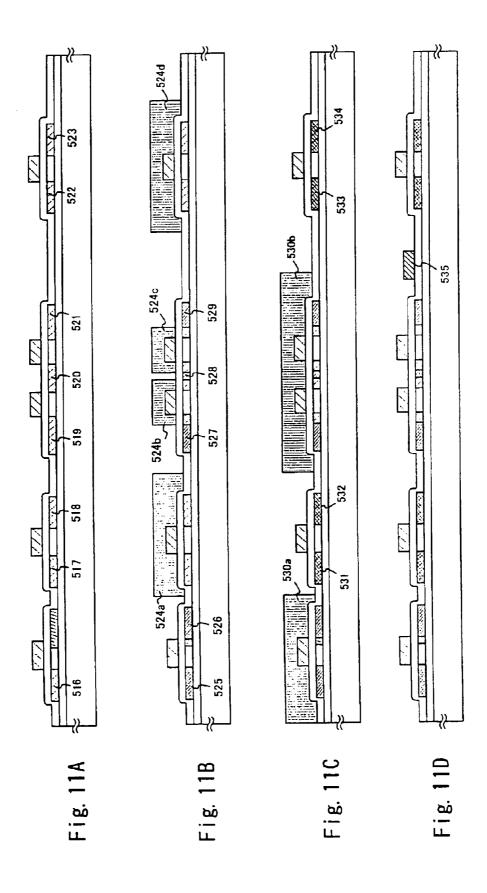

FIGS. 10A to 10E are diagrams showing a process of

FIGS. 11A to 11D are diagrams showing the process of manufacturing the EL display of the present invention;

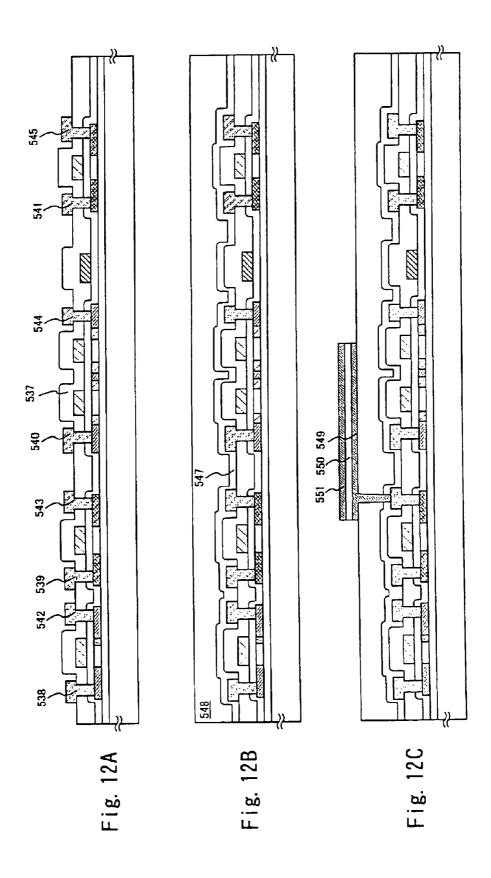

FIGS. 12A to 12C are diagrams showing the process of manufacturing the EL display of the present invention;

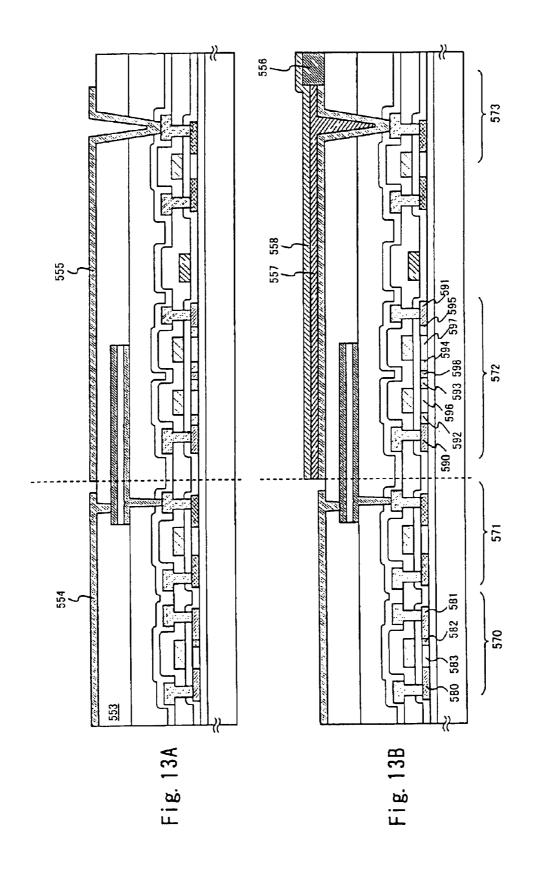

FIGS. 13A and 13B are diagrams showing the process of manufacturing the EL display of the present invention;

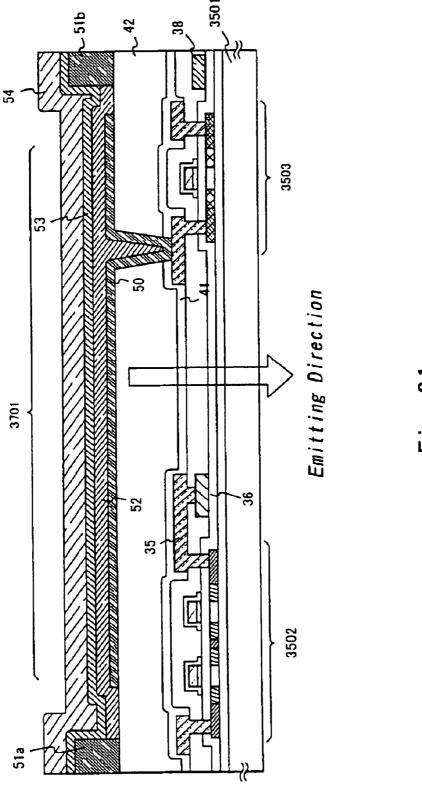

FIG. 14 is a cross sectional diagram of an EL display of the present invention;

FIG. 15 is a circuit diagram of a sensor pixel of an EL display of the present invention;

FIG. 16 is a cross sectional diagram of an EL display of

the present invention; FIGS. 17A and 17B are external views of an EL display

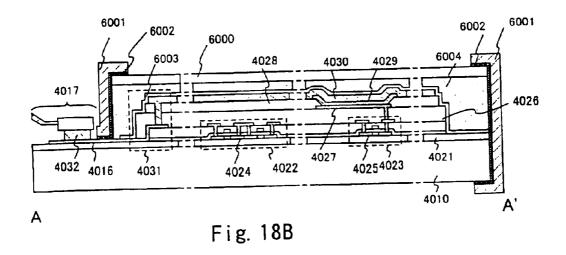

of the present invention; FIGS. 18A and 18B are external views of an EL display

of the present invention;

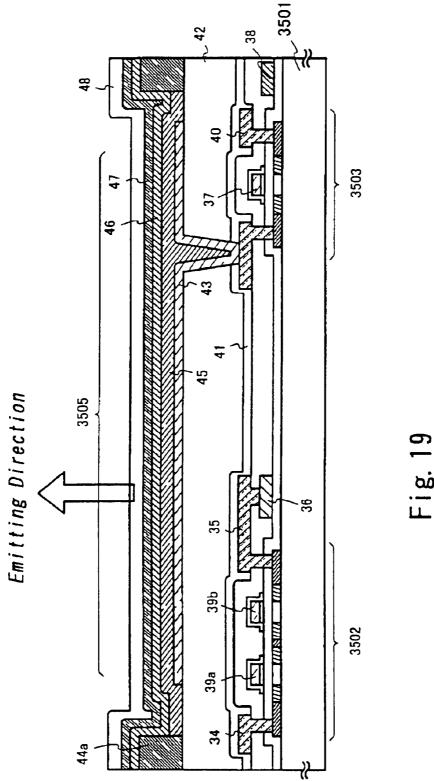

FIG. 19 is a cross sectional diagram of a display pixel of an EL display of the present invention;

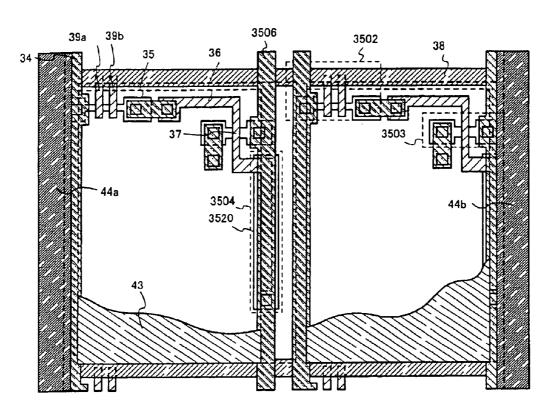

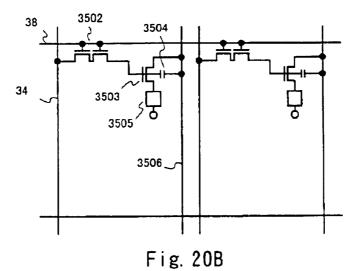

FIGS. 20A and 20B are a top view and a circuit diagram, respectively, of a display pixel of an EL display of the present invention;

FIG. 21 is a cross sectional diagram of a display pixel of an EL display of the present invention;

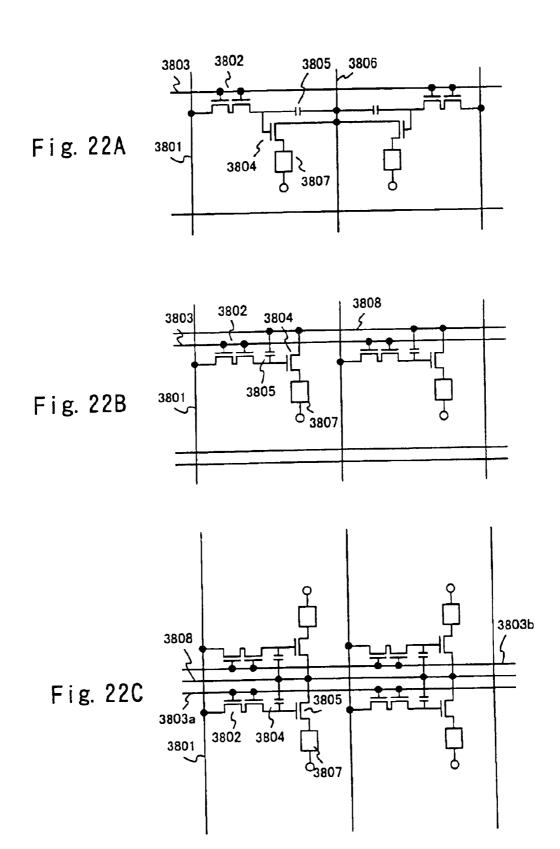

FIGS. 22A to 22C are circuit diagrams of a display pixel of an EL display of the present invention;

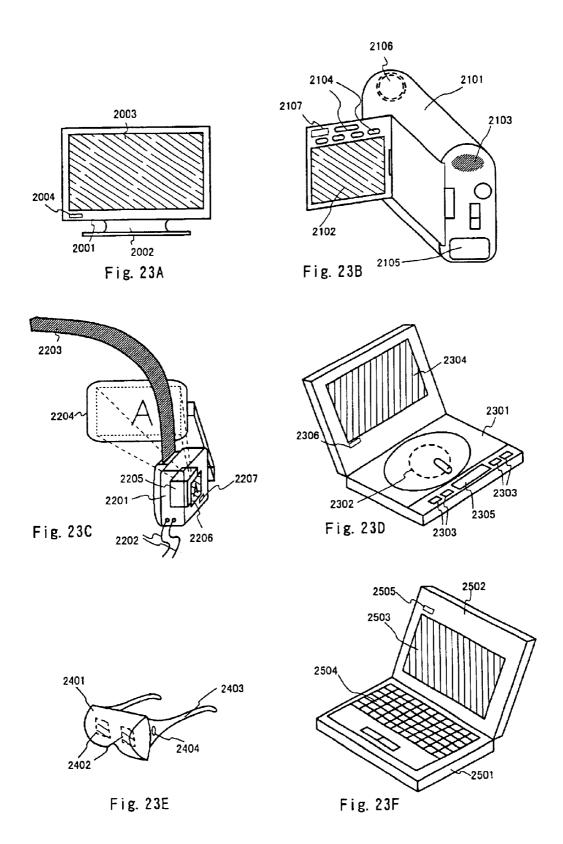

FIGS. 23A to 23F are diagrams showing examples of <sup>5</sup> electronic equipment using an EL display of the present invention:

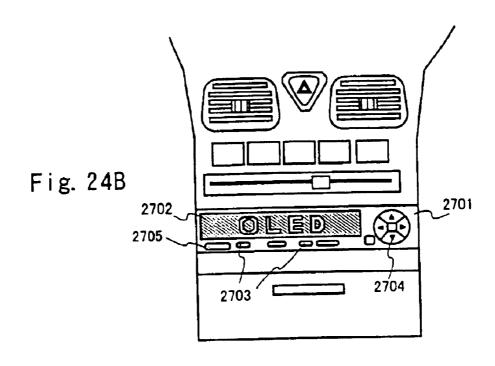

FIGS. 24A and 24B are diagrams of electronic equipments using an EL display of the present invention; and

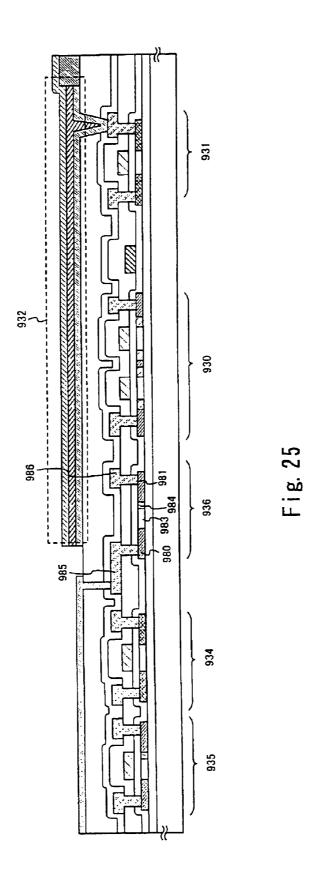

FIG. 25 is a cross sectional diagram of an EL display of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

An embodiment mode of the present invention will be explained with reference to FIGS. 1 to 6.

Shown in FIG. 1 is a top view of an EL display, which is a portion of a semiconductor display device of the present invention. It is to be noted that in the embodiment mode of the present invention, an explanation will be made on an EL display for performing color display that is driven by a digital method. However, the driving method of the EL display of the present invention is not limited to the digital method, and the EL display may be driven by an analog method. In addition, although an explanation is made in the embodiment mode on the EL display for performing color display, the EL display of the present invention may performs not only color display, but also monochrome display.

As shown in FIG. 1, there is provided a display portion 101, a source signal line driver circuit 102, a gate signal line driver circuit 103, and a sensor portion 106. The source signal line driver circuit 102 is composed of a shift register 102a, a latch (A) 102b, and a latch (B) 102c.

The sensor portion 106 has sensor pixels 104 (R sensor pixel 104a, G sensor pixel 104b, and B sensor pixel 104c) that correspond to the colors RGB, respectively. Note that an EL display of a color display system that employs three kinds of EL elements corresponding to the colors RGB is illustrated in the embodiment mode. However, the present invention is not limited thereto, and an EL display of a color display system that employs an EL element emitting white light may be used. Further, in the embodiment mode, although the sensor portion 106 has 3 sensor pixels that correspond to the colors RGB, respectively, the present invention is not limited thereto. Only sensor pixels that correspond to 1 or 2 colors of the colors RGB may be provided in the sensor portion.

A detailed circuit diagram of the display portion 101 and 50 the sensor portion 106 is shown in FIG. 2. Source signal lines (S1 to Sx), power source supply lines (V1 to Vx), and gate signal lines (G1 to Gy) are provided in the display portion 101. Note that the sensor portion 106 and the display portion 101 are provided on the same substrate in the 55 embodiment mode. However, the present invention is not limited thereto. The structure may be such that the sensor portion and the display portion are provided on different substrates and connected by an FPC or the like.

The display portion 101 includes a plurality of display 60 pixels 105. The display pixels 105 each have any one of the source signal lines (S1 to Sx), any one of the power source supply lines (V1 to Vx), and any one of the gate signal lines (G1 to Gy). There are 3 types of display pixels 105: a display pixel for displaying the color R; a display pixel for displaying the color R

6

A source signal line Sp (where p is an arbitrary number between 1 and x), a power source supply line Vp, and a gate signal line Gq (where q is an arbitrary number between 1 and y) are contained in an arbitrarily selected display pixel (p, q) of the display pixels for displaying the color R. Also, similar to the display pixel (p, q) for displaying the color R, the source signal line Sp, the power source supply line Vp, and the gate signal line Gq are contained in the R sensor pixel 104a.

Though not shown in the figure, similarly, the same source signal line, power source supply line, and gate signal line that are included in an arbitrarily selected display pixel for displaying the color G are also contained in the G sensor pixel 104b. Likewise not shown in the figure, the same source signal line, power source supply line, and gate signal line that are contained in an arbitrarily selected display pixel for displaying the color B are also contained in the B sensor pixel 104c.

A detailed structure of the sensor pixels 104a to 104c is shown in FIG. 3. A region that is surrounded by a dotted line is the sensor pixel 104. Contained in the sensor pixel 104 are a source signal line S (any one of the lines between S1 and Sx), a power source supply line V (any one of the lines between V1 and Vx), and a gate signal line G (any one of the lines between G1 and Gy).

In addition, the sensor pixel **104** (**104***a* to **104***c*) has a switching TFT **130**, an EL driving TFT **131**, and a sensor EL element **132**. A capacitor **133** is provided in the structure of FIG. **3**, but the structure may be formed without the provision of the capacitor **133**.

The sensor EL element 132 is composed of an anode, a cathode, and an EL layer provided therebetween. When the anode is connected to a drain region of the EL driving TFT 131, in other words, when the anode is a pixel electrode, the cathode serving as an opposing electrode is held at a predetermined electric potential (opposing electric potential). On the other hand, when the cathode is connected to the drain region of the EL driving TFT 131, in other words, when the cathode is the pixel electrode, then the anode serving as the opposing electrode is held at a predetermined electric potential (opposing electric potential).

A gate electrode of the switching TFT 130 is connected to the gate signal line G. One of a source region and a drain region of the switching TFT 130 is connected to the source signal line S, and the other is connected to a gate electrode of the EL driving TFT 131.

One of a source region and the drain region of the EL driving TFT 131 is connected to the power source supply line V, and the other is connected to the sensor EL element 132. The capacitor 133 is provided so as to be connected to the gate electrode of the EL driving TFT 131 and the power source supply line V.

Further, the sensor pixel 104 has a reset TFT 134, a buffer TFT 135, and a light, receiving diode 136.

A gate electrode of the reset TFT 134 is connected to a reset signal line RL. A source region of the reset TFT 134 is connected to a sensor power source line VB and a drain region of the buffer TFT 135. The sensor power source line VB is constantly held at a fixed electric potential (standard electric potential). Further, a drain region of the reset TFT 134 is connected to the light receiving diode 136 and a gate electrode of the buffer TFT 135.

A source region of the buffer TFT 135 is connected to a sensor output wiring FL. The sensor output wiring FL is further connected to a constant-current power source 137 and a fixed current constantly flows therein. Further, the

drain region of the buffer TFT 135 is connected to the sensor power source line VB which is constantly maintained at a fixed standard electric potential. The buffer TFT 135 functions as a source follower.

Although not shown in the figure, the light receiving <sup>5</sup> diode **136** is composed of a cathode, an anode, and a photoelectric converting layer provided therebetween.

Shown in FIG. 4 is a detailed structure of the display pixel 105. An area surrounded by a dotted line is the display pixel 105. The source signal line S (any one of the lines between S1 and Sx), the power source supply line V (any one of the lines between V1 and Vx), and the gate signal line G (any one of the lines between G1 and Gy) are contained in the display pixel 105.

Similar to the sensor pixel 104, the display pixel 105 has a switching TFT 140, an EL driving TFT 141, and a display EL element 142. The display EL element 142 has the same structure as that of the sensor EL element 132 that is shown in FIG. 3. To be more specific, the display EL element 142 and the sensor EL element 132 each have an EL layer sandwiched between a pair of electrodes. In addition, the material constructing the pair of electrodes and the laminate structure of the EL layer are at least respectively the same for both the EL elements. In particular, when the color of light emitted by the sensor EL element 132 and the display EL element 142 is the same, then the material (EL material) that forms the EL layer is also the same.

The display EL element 142 is composed of an anode, a cathode, and an EL layer provided therebetween. When the anode is connected to a drain region of the EL driving TFT 141, in other words, when the anode is a pixel electrode, the cathode serving as an opposing electrode is held at a predetermined electric potential (opposing electric potential). On the other hand, when the cathode is connected to the drain region of the EL driving TFT 141, in other words, when the cathode is the pixel electrode, then the anode serving as the opposing electrode is held at a predetermined electric potential (opposing electric potential).

Further, a capacitor 143 is provided in the structure of 40 FIG. 4, but the structure may be formed without the provision of the capacitor 143.

A gate electrode of the switching TFT **140** is connected to the gate signal line G. One of a source region and a drain region of the switching TFT **140** is connected to the source signal line S, and the other is connected to a gate electrode of the EL driving TFT **141**.

One of a source region and the drain region of the EL driving TFT 141 is connected to the power source supply line V, and the other is connected to the display EL element 142. The capacitor 143 is provided so as to be connected to the gate electrode of the EL driving TFT 141 and the power source supply line V.

Next, a description will be made on a driving method of the EL display of the embodiment mode.  $_{55}$

FIG. 1 is referenced. In the source signal line driver circuit 102, a clock signal (CLK) and a start pulse (SP) are inputted to the shift register 102a. The shift register 102a sequentially generates timing signals on the basis of the clock signal 60 (CLK) and the start pulse (SP) to thereby sequentially feed the timing signals to downstream circuits.

The timing signals from the shift register 102a are current-amplified by a buffer (not shown) or the like, and the current-amplified timing signals may be sequentially fed to 65 the downstream circuits. A large number of circuits or elements are connected to the wiring through which the

8

timing signals are fed, so that the load capacitance (parasitic capacitance). The buffer is provided to prevent the sharpness of the rise or fall of the timing signals from being reduced by this large load capacitance.

The timing signals from the shift register 102a are then fed to the latch (A) 102b. The latch (A) 102b has a plurality of stages of latches for processing n-bit digital video signals. The latch (A) 102b sequentially writes in and holds the n-bit digital video signals including image information upon input of the timing signals.

Note that the digital video signals may be sequentially fed to the plural stages of the latches of the latch (A) 102b when the digital video signals are taken in by the latch (A) 102b. However, the present invention is not limited to this structure. A so-called division drive may be performed in which the plural stages of latches of the latch (A) 102b are divided into a number of groups and then the digital video signals are parallely fed to the respective groups at the same time. It is to be noted that the number of groups at this point is called a division number. For example, if the latches are grouped into 4 stages each, then it is called a 4-branch division drive.

The time necessary to complete writing of the digital video signals into all the stages of the latches of the latch (A) 102b is called a line period. In other words, the line period is defined as a time interval from the start of writing the digital video signals into the latch of the leftmost stage to the end of writing the digital video signals into the latch of the rightmost stage in the latch (A) 102b. In practice, a line period may be a period in which a horizontal return period is added to the above line period.

After the completion of one line period, a latch signal is fed to the latch (B) 102c. At this moment, the digital video signals written in and held by the latch (A) 102b are sent all at once to the latch (B) 102c to be written in and held by all the stages of latches thereof.

Sequential writing-in of digital video signals on the basis of the timing signals from the shift register 102a is again carried out to the latch (A) 102b after it has completed sending the digital video signals to the latch (B) 102c.

During this second time one line period, the digital video signals written in and held by the latch (B) 102b are inputted to source signal lines.

On the other hand, the gate signal line driver circuit 103 is composed of a shift register and a buffer (both not shown in the figure). Depending on the situation, the gate signal line driver circuit 103 may have a level shifter beside the shift register and the buffer.

In the gate signal line driver circuit 103, the timing signals from the shift register (not shown in the figure) are fed to the buffer (not shown in the figure) to be fed to corresponding gate signal lines (also referred to as scanning lines). The gate signal lines are connected to the gate electrodes of the switching TFTs of one line, and all the switching TFTs of one line have to be turned ON simultaneously. Therefore, the use of a buffer with a large electric current capacity is required.

It is to be noted that the structure, the driving method, and the number of the source signal line driver circuit 102 and the gate signal line driver circuit 103 are not limited to the structure in the embodiment mode.

Shown in FIG. 5 is a timing chart illustrating a case where the EL display of the present invention is driven by the digital method to perform a display.

First, a 1 frame period (F) is divided into an "n" number of sub-frame periods (SF1 to SFn). Note that a period in

which all the pixels in the pixel portion display 1 image is referred to as the 1 frame period (F).

The provision of 60 or more frame periods within one second by the EL display is preferred. The glimmering of images such as flickering may be visually suppressed by providing the number of images displayed in one second to be 60 or more.

Note that a period in which 1 frame period is divided into a plurality of periods is referred to as sub-frame period (SF). As the number of tones increase, the number of sub-frame 10 periods in 1 frame period also increases.

The subframe periods are divided into address periods (Ta) and sustain periods (Ts). The address period is a period required for inputting digital video signals into all of the pixels during one subframe period, and the sustain period (also referred to as a turn on period) denotes a period in which the EL element is made to either emit light or not to thereby perform display by the digital video signals inputted to the pixels in the address period.

The address periods (Ta) of SF1 to SFn are Ta1 to Tan,  $^{20}$  respectively. The sustain periods (Ts) of SF1 to SFn are Ts1 to Tsn, respectively.

The electric potential of the power source supply lines (V1 to Vx) is maintained at a predetermined electric potential (power source electric potential).

First, in the address period Ta, the electric potential of the opposing electrodes of both the display EL element **142** and the sensor EL element **132** is maintained at a level equivalent to the power source electric potential.

Then, a gate signal is fed to the gate signal line G1. Among the plural number of switching TFTs 140 of the display pixels 105 and the plural number of switching TFTs 130 of the sensor pixels 104, all the switching TFTs connected to the gate signal line G1 are turned into the ON state. Note that throughout this specification, a TFT in the ON state is referred to as driving of a TFT.

Next, the digital video signals from the source signal line driver circuit 102 are fed to the source signal lines (S1 to Sx) in the state that all the switching TFTs connected to the gate signal line G1 are turned into the ON state. The digital video signals have the information [0] or [1]. The digital video signals [0] and [1] are signals where one has a "Hi" (High) voltage while the other has an "Lo" (Low) voltage.

Then via the switching TFTs that are in the ON state, the digital video signals that are fed to the source signal lines (S1 to Sx) are fed to the gate electrode of the EL driving TFT, which is connected to the source region or the drain region of the switching TFTs.

Next, the gate signal is fed to the gate signal line G2, 50 whereby all the switching TFTs 1501 that are connected to the gate signal line G2 turn into the ON state. Among the plural number of switching TFTs 140 of the display pixels 105 and the plural number of switching TFTs 130 of the sensor pixels 104, all the switching TFTs connected to the 55 gate signal line G2 are turned into the ON state.

The digital video signals from the source signal line driver circuit 102 are then fed to the source signal lines (S1 to Sx) in the state that all the switching TFTs connected to the gate signal line G2 are turned into the ON state. Then via the 60 switching TFTs that are in the ON state, the digital video signals that are fed to the source signal lines (S1 to Sx) are fed to the gate electrode of the EL driving TFT, which is connected to the source region or the drain region of the switching TFTs.

The above-described operation is repeated until the gate signal is fed to the gate signal line Gy to thereby input the 10

digital video signals to all the display pixels 105 and the sensor pixels 104. A period until the completion of inputting the digital video signals to all the display pixels 105 and the sensor pixels 104 is the address period. Note that the lengths of the respective address periods (Ta1 to Tan) of the "n" number of sub-frame periods are all the same.

Upon the completion of the address period Ta, a sustain period begins. In the sustain period, the electric potential of all the opposing electrodes of the EL elements is set to a level where it has an electric potential difference with the power source electric potential to the extent that the EL element emits light when the power source electric potential is applied to the pixel electrode.

Thereafter, in the sustain period, all the switching TFTs of the display pixels 105 and the sensor pixels 104 are turned into the OFF state. The digital video signal fed to the display pixels 105 and the sensor pixels 104 is then fed to the gate electrode of the EL driving TFT of each of the pixels.

In the embodiment mode, when the digital video signal has the information [0], then the EL driving TFT is turned into the OFF state. Therefore, the pixel electrode of the EL element is in the state of being maintained at the electric potential of the opposing electrode. As a result, the EL element of the pixel to which the digital video signal having the information [0] is inputted does not emit light.

On the other hand, when the digital video signal has the information [1], then the EL driving TFT is turned into the ON state in the embodiment mode. Therefore, the power source electric potential is applied to the pixel electrode of the EL element. As a result, the EL element of the pixel to which the digital video signal having the information [1] is inputted emits light.

Thus, the EL element either emits light or not depending on the information of the digital video signal to the pixels, whereby the pixels perform display.

Upon completion of the sustain period, 1 subframe period ends. Then the next subframe period appears and turns into an address period again. At the point the digital video signals have been fed to all the pixels, a sustain period begins again. It is to be noted that the order of appearance of the sub-frame periods is arbitrary.

The same operation is repeated in the rest of the sub-frame periods to thereby perform display. Upon the completion of the "n" number of sub-frame periods, 1 frame period ends.

Further, in the present invention, a ratio of the lengths of the "n" number of sustain periods Ts1, . . . , Tsn is expressed as Ts1: Ts2: Ts3: . . . : Ts(n-1): Tsn= $2^0$ :  $2^{-1}$ :  $2^{-2}$ : . . . :  $2^{-(n-2)}$ :  $2^{-(n-1)}$ .

The gradation of each pixel is determined by which subframe period is selected for light emission during one frame period. For example, if n=8, and the luminance of pixels having light emitted during all of the sustain periods is taken as 100%. then in case of the pixels emitting light in Ts1 and Ts2, the luminance is expressed as 70%, and when Ts3, Ts5, and Ts8 are selected, the luminance can be expressed as 16%.

Note that in the embodiment mode, the EL element did not emit light because the electric potential of the opposing electrode was maintained at an electric potential that is equivalent to the power source electric potential in the address period. However, the present invention is not limited to this structure. An electric potential difference to the extent that EL element emit light when the power source electric potential is applied to the pixel electrode is constantly provided between the opposing electric potential and the

power source electric potential. Thus, the address period, similarly to the display period, may also perform display. However, in this case, all the subframe periods actually become periods performing display, and therefore, the lengths of the subframe periods are set at SF1: SF2: SF3: . . . : SF(n-1): SFn= $2^0$ :  $2^{-1}$ :  $2^{-2}$ : . . . :  $2^{-(n-2)}$ :  $2^{-(n-1)}$ . By adopting the above structure, a high luminance image can be attained compared with the driving method where the address periods do not emit light.

As explained above, simultaneously with the display of an 10 image in the display portion depending on the luminescent or non-luminescent state of the display EL elements, similar to the display EL elements, the sensor EL elements become either luminescent or non-luminescent state.

Next, an explanation will be made on the mechanism of  $^{15}$ the light receiving diode 136 detecting the luminance of the sensor EL element 132 in the sensor portion 106.

It is desirable that one of the reset TFT 134 and the buffer TFT 135 of the sensor pixel 104 is an n-channel TFT, and the remaining one is a p-channel TFT.

First, the reset TFT 134 is turned into the ON state depending on a reset signal that is fed to the rest signal line RL. Therefore, the standard electric potential of the sensor power source line VB is applied to gate electrode of the buffer TFT 135. The source region of the buffer TFT 135 is connected to the constant-current power source via the sensor output wiring FL, whereby the electric potential difference  $V_{GS}$  of the gate electrode and the source region of the buffer TFT 135 is constantly at a fixed value. Accordingly, the source region of the buffer TFT 135 is held at an electric potential where  $V_{GS}$  is subtracted from the standard electric potential. Note that in this specification, a period in which the reset TFT 134 is in the ON state is referred to as a reset period.

Next, the electric potential of the reset signal that is fed to the reset signal line RL is changed, whereby the reset TFT 134 is turned into the OFF state. Therefore, the standard electric potential of the sensor power source line VB is not applied to the gate electrode of the buffer TFT 135. Note that a period in which the reset TFT 134 is in the OFF state is referred to as a sample period in this specification.

In case of the EL display being driven by the digital method, the sample period is longer than the address period Ta and overlaps the sustain period Ts in which the sensor EL 45 element 132 is emitting light.

The irradiation of the light generated from the sensor EL element 132 to the light receiving diode 136 makes a current flow in the light receiving diode 136. Therefore, the fixed electric potential of the gate electrode of the buffer TFT 135 in the reset period changes in the sample period. The amount of the change in the electric potential will alternates on the basis of the size of the current flowing in the light receiving diode 136.

The current flowing in the light receiving diode 136 is 55 proportional to the strength of the light irradiated thereto. In other words, compared with when the luminance of the sensor EL element 132 is high and when the luminance thereof is low, a larger current flows to the light receiving diode 136 when the luminance thereof is high. 60 source 206 to each of the colors to be revised. In other Consequently, the electric potential of the gate electrode of the buffer TFT 135 undergoes a large change when the luminance 6f the sensor EL element 132 is high compared with when the luminance thereof is low.

Because the electric potential difference  $V_{GS}$  of the source 65 region and the gate electrode of the buffer TFF 135 is always a fixed value, the electric potential of the source region of the

buffer TFT 135 is maintained at an electric potential in which V<sub>GS</sub> is subtracted from the electric potential of the gate electrode thereof. Thus, when the electric potential of the gate electrode of the buffer TFT 135 changes, the electric potential of the source region of the buffer TFT 135 changes together therewith.

The electric potential of the source region of the buffer TFT 135 is applied to the sensor output wiring FL to thereby be fed to a correction circuit as a sensor output signal.

Shown in FIG. 6 is the block diagram of a correction circuit 201. The correction circuit 201 may be provided on the same substrate with the display portion 101 or the sensor portion 106. Further, it may be provided on an IC chip and be connected to the sensor portion 106 by an FPC or the like.

The correction circuit 201 is composed of an A/D converter circuit 202, a arithmetic circuit 203, a correction memory 204, and a D/A converter circuit 205. Note that although the structure of FIG. 6 shows a case where the correction memory 204 is constructed as a part of the arithmetic circuit 203, the correction memory 204 and the arithmetic circuit 203 may be provided separately.

The sensor output signal from the sensor output wiring FL is fed to the A/D converter circuit 202 to thereby be converted into a digital sensor output signal and be outputted therefrom. The digital sensor output signal outputted from the A/D converter circuit 202 is then fed to the arithmetic circuit 203.

When the sensor EL element 132 has an ideal luminance, the data of the digital sensor output signal (correction standard data) that is to be fed to the arithmetic circuit 203 is stored in the correction memory 204.

The arithmetic circuit 203 compares the digital sensor output signal that was actually fed to the arithmetic circuit 203 with the correction standard data stored in the correction memory 204. Then the arithmetic circuit 203 calculates, from the difference between the actual sensor output signal and the correction standard data that were compared, the level of the electric potential (power source electric potential) of the power source supply line V necessary for the display EL element 142 and the sensor E1 element 132 to obtain an ideal luminance. Thereafter, the arithmetic circuit 203 feeds the digital correction signal having the information of the level of the power source electric potential to the D/A converter circuit 205.

The digital correction signal that is fed to the D/A converter circuit 205 is converted into an analog signal to thereby be fed to an EL power source 206. The EL power source 206 applies an electric potential whose level is determined by the inputted analog correction signal to the power source supply lines (V1 to Vx). In case the luminance of the EL element is reduced, the correction mechanism works by regulating the power source electric potential of the power source supply lines so as to supplement the reduction thereof to thereby enhance the luminance of the EL element.

Note that when the EL display employs the three kinds of EL elements corresponding to the colors RGB, it is necessary to provide the correction circuit 201 and the EL power words, in case of revising each of the colors RGB, the provision of 3 correction circuits 201 and 3 EL power sources 206 is necessary.

Furthermore, when the EL display employs an EL element emitting a single color such as white, blue, or blue-green, the provision of the correction circuit 201 and the EL power source 206 may be one of each, or the provision thereof may

be for each color to be revised. The deterioration rate of the EL layer differs depending on the wavelength of the light irradiated thereto. Therefore, in case of the EL display employing the EL element emitting white light and a color filter, by providing the correction circuit 201 and the EL 5 power source 206 to each of the colors to be revised, a more accurate correction can be made to the luminance of the EL element corresponding to each of the colors. As a result, a clearer image of a desirable color as well can be displayed.

In the present invention, by adopting the above structure, <sup>10</sup> the display EL element **142** and the sensor EL element **132** are capable of having an ideal luminance, thereby making it possible for the EL display to perform a clear and desirable color display even if the EL layer in the EL display deteriorates. <sup>15</sup>

Note that although the sensor portion has one of the sensor pixels corresponding to the respective colors RGB in the embodiment mode, the present invention is not limited thereto. A plurality of sensor pixels corresponding to each of the colors may be provided.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Embodiments of the present invention are explained below.

Embodiment 1

An EL display of the present invention driven by an analog method is explained in Embodiment 1 using FIGS. 7 to 9.

Shown in FIG. 7 is a top view of an EL display, which is 30 a portion of a semiconductor display device of the present invention. In Embodiment 1, an explanation will be made on an EL display for performing color display. However, the EL display of the present invention not only performs color display but may also perform monochrome display.

As shown in FIG. 7, there is provided a display portion 301, a source signal line driver circuit 302, a gate signal line driver circuit 303, and a sensor portion 306. The source signal line driver circuit 302 is composed of a shift register 302a, a level shifter 302b, and a sampling circuit 302c.

The sensor portion 306 has sensor pixels 304 (R sensor pixel 304a, G sensor pixel 304b, and B sensor pixel 304c) that correspond to the colors RGB, respectively. Note that an EL display of a color display system that employs three kinds of EL elements corresponding to the colors RGB is illustrated in Embodiment 1. However, Embodiment 1 is not limited thereto, and an EL display of a color display system that employs an EL element emitting white light may be used. Further, although the sensor portion 306 shown in Embodiment 1 has 3 sensor pixels that correspond to the colors RGB, respectively, the present invention is not limited thereto. Only sensor pixels that correspond to 1 or 2 colors of the colors RGB may be provided in the sensor portion.

The detailed structure of the display portion 301 and the 55 sensor portion 306 is the same as for a case of driving by a digital method, and therefore, FIG. 2 is referenced. Note that the display portion 301, the sensor portion 306, the R sensor pixel 304a, the G sensor pixel 304b, and the B sensor pixel 304c, all of FIG. 7, correspond to the display portion 101, 60 the sensor portion 106, the R sensor pixel 104a, the G sensor pixel 104b, and the B sensor pixel 104c, respectively, of FIG. 2.

Note that, in Embodiment 1, the sensor portion and the display portion are formed on the same substrate, but the 65 present invention is not limited thereto. A structure may be such that the sensor portion and the display portion are

14

formed on different substrates and connected by a connector such as an FPC.

The display portion 301 includes a plurality of display pixels. Note that the display pixels in Embodiment 1 correspond to the display pixels 105 in FIG. 2. The display pixels 105 each have any one of source signal lines (S1 to Sx), any one of power source supply lines (V1 to Vx), and any one of gate signal lines (G1 to Gy). There are 3 types of display pixels: a display pixel for displaying the color R; a display pixel for displaying the color G; and a display pixel for displaying the color B.

A source signal line Sp (where p is an arbitrary number between 1 and x), a power source supply line Vp, and a gate signal line Gq (where q is an arbitrary number between 1 and y) are contained in an arbitrarily selected display pixel (p, q) for displaying the color R. Also, similar to the display pixel (p, q), the source signal line Sp, the power source supply line Vp, and the gate signal line Gq are contained in the R sensor pixel 304a.

Also, the same source signal line, power source supply line, and gate signal line that are included in an arbitrarily selected display pixel for displaying the color G are also contained in the G sensor pixel 304b. Further, the same source signal line, power source supply line, and gate signal line that are contained in an arbitrarily selected display pixel for displaying the color B are also contained in the B sensor pixel 304c. The structures of the display pixel and the sensor pixel 304 are the same as for the case of driving by the digital method of FIG. 3 and FIG. 4, and therefore the embodiment mode may be referenced for an explanation of the structures.

Next, a description will be made on a driving method of an EL display of Embodiment 1.

FIG. 7 is referenced. In the source signal line driver circuit 302, a clock signal (CLK) and a start pulse (SP) are inputted to the shift register 302a. The shift register 302a sequentially generates timing signals on the basis of the clock signal (CLK) and the start pulse (SP) to thereby sequentially feed the timing signals to downstream circuits.

A timing signal from the shift register 302a has its voltage amplitude made larger in the level shifter 302b, and is inputted to the sampling circuit 302c. The sampling circuit 302c, in synchronous with the timing signal, then samples the signal having analog image information (analog video signal) in accordance with an analog switch, and the sampled signal is inputted to a corresponding source signal line

Note that the source signal line driver circuit 302 may have a buffer. A large number of circuits or elements are connected to the wiring through which the timing signals are fed, so that the load capacitance (parasitic capacitance) due to those circuits or elements is large. The buffer is effective to prevent the sharpness of the rise or fall of the timing signals from being reduced due to this large load capacitance.

On the other hand, the gate signal line driver circuits 303 each have a shift register and a buffer (neither shown in the figures). Further, the gate signal line driver circuits 303 also may have level shifter circuits other than a shift register and a buffer.

The timing signal is supplied to the buffer (not shown in the figure) from the shift register (not shown in the figure) in the gate signal line driver circuit 303, and is then supplied to a corresponding gate signal line (also referred to as a scanning line). The gate electrodes of the switching TFT for one line are connected to the gate signal line, and all of the switching TFTs for one line must be turned ON simulta-

neously. Therefore, a buffer capable of handling a large electric current flow is used.

Note that the number of the source signal line driver circuits **302** and the gate signal line driver circuits **303**, the circuit structures, and the methods of driving the circuits are not limited to the constitution shown in Embodiment 1.

Next, a timing chart for a case of driving the EL display of the present invention by the analog method is shown in FIG. 8. A period from the selection of one gate signal line in accordance with a gate signal until a different gale signal line 10 is next selected is referred to as one line period (L). Further, a period from display of one image until display of the next image is referred to as one frame period (F). When there are y gate signal lines, there are y line periods (L1 to Ly) formed within one frame period.

First, power source supply lines (V1 to Vx) are maintained at a predetermined electric power source potential. An opposing electrode is also maintained at a predetermined electric potential. The electric potential of the opposing electrode has an electric potential difference with the electric 20 power source potential to the extent that an EL element emits light when the electric power source potential is applied to a pixel electrode.

Aselection signal is inputted to a gate signal line G1 in the first line period L1 from the gate signal line driver circuit 25 303. The sampled analog video signal is then inputted to source signal lines (S1 to Sx). All of the switching TFTs connected to the gate signal line G1 is turned ON in accordance with the selection signal, and therefore, the analog video signal inputted to the source signal lines is 30 inputted to the gate electrodes of the EL driving TFTs through the switching TFTs.

The amount of electric current flowing in a channel forming region of the EL driving TFT is controlled by the height (voltage) of the electric potential of the signal input- 35 ted to its gate electrode. The height of the electric potential of the pixel electrode of the EL element is therefore determined by the electric potential of the analog signal inputted to the gate electrode of the EL driving TFT. The EL element is then controlled by the electric potential of the analog 40 video signal and emits light.

The above-stated operations are repeated, and when the analog video signal is inputted to the source signal lines (S1 to Sx), the first line period L1 ends. Note that the period until completion of analog video signal inputted to the source 45 signal lines (S1 to Sx) may also be taken together with a horizontal return period as one line period. The second line period L2 then begins, and the selection signal is inputted to the gate signal line G2. Then, similar to the first line period L1, the analog video signal is inputted to the source signal 50 lines (S1 to Sx) in order.

When the selection signal is inputted to all of the gate signal lines (G1 to Gy), all of the line periods (L1 to Ly) are completed. One frame period is complete when all of the line periods (L1 to Ly) are complete. Display is performed 55 in all of the pixels within one frame period, and one image is formed. Note that all of the line periods (L1 to Ly) may be taken together with a vertical return period as one frame period.

The luminance of the EL elements is thus controlled in 60 accordance with the electric potential of the analog video signal inputted to the source signal lines, as above. Gray-scale display is performed in accordance with the control of luminance.

An explanation of how the luminance of display EL 65 elements and the luminance of sensor EL elements are corrected in accordance with a sensor output signal output-

16

ted from the sensor portion 306 is explained next using FIG. 9. Note that a light receiving diode detects the luminance of the sensor EL elements in the sensor pixel shown in FIG. 7. The processes until the sensor output signal is inputted to a sensor output wiring is the same as for the case of the digital drive EL display shown in the embodiment mode, and therefore, the explanation is omitted.

The sensor output signal having luminance information of the sensor EL element detected by the light receiving diode is inputted to a video signal correction circuit through a sensor output wiring FL in a sampling period.

A block diagram of a video signal correction circuit 401 is shown in FIG. 9. The video signal correction circuit 401 may be formed on the same substrate as the display portion 301 and the sensor portion 306, and it may also be formed on an IC chip and connected to the sensor portion 306 by an FPC or the like.

The video signal correction circuit 401 has an A/D converter circuit 402, an arithmetic circuit 403, a correction memory 404, and a D/A converter circuit 405. Note that a structure for a case in which the correction memory 404 is a portion of the arithmetic circuit 403 is shown in FIG. 9, but the correction memory 404 and the arithmetic circuit 403 may also be formed separately.

A signal generator 406 generates a signal having digital image information (digital video signal), and this is inputted to the arithmetic circuit 403. Note that when the signal having image information and output from the signal generator 406 (video signal) is analog, the signal is first converted to a digital video signal by the A/D converter circuit and then is inputted to the arithmetic circuit 403.

The sensor output signal is inputted to the A/D converter circuit 402 from the sensor output wiring FL, is converted into a digital sensor output signal, and is then outputted. The digital sensor output signal outputted from the A/D converter circuit 402 is then inputted to the arithmetic circuit 403.

When the display EL elements and the sensor EL elements have ideal luminances, the digital sensor output signal data inputted to the arithmetic circuit 403 (correction standard date) is stored in the correction memory 404.

The arithmetic circuit 403 compares the actual digital sensor output signal inputted to the arithmetic circuit 403 with the correction standard data stored in the correction memory 404. Then, based upon the comparative difference between the actual sensor output signal and the correction standard data, the digital video signal inputted to the arithmetic circuit 403 from the signal generator 406 is corrected. Note that it is very important that the digital video signal after correction at this time has the necessary electric potential in order to obtain ideal luminance levels in the display EL elements and the sensor EL elements when converted to analog.

Note that a sensor output signal corresponding to each display color is inputted to the arithmetic circuit 403. For example, the three sensor output signals outputted from the R sensor pixel 304a, the G sensor pixel 304b, and the B sensor pixel 304c are inputted to the arithmetic circuit 403 in Embodiment 1. The digital video signal is corrected such that an analog video signal having a desired height electric potential is sampled and inputted to pixels corresponding to each color (the display pixels and the sensor pixels).

The corrected digital video signal is next inputted to the D/A converter circuit 405 from the arithmetic circuit 403. The corrected digital video signal inputted to the D/A converter circuit 405 is converted to analog, and is then inputted to the sampling circuit 302c of the source signal line

driver circuit 302 as an analog video signal. The analog video signal has a necessary electric potential in order to obtain the ideal luminance in the display EL elements and the sensor EL elements.

According to the above structure, in the present invention, 5 the display EL elements and the sensor EL elements can have ideal luminances, even if the EL layer in the EL display deteriorates, and it becomes possible to perform the desired color display with clarity.

Note that the sensor portion has one each of sensor pixels 10 corresponding to R, G, and B in Embodiment 1, but the present invention is not limited to this. A plurality of sensor pixels corresponding to each color may also exist.

Further, by correcting the electric potential of the analog video signal inputted to the display portion in the video 15 signal correction circuit, the luminance of the EL elements is corrected with the analog drive EL display of Embodiment 1. However, the present invention is not limited to this. In addition to correcting the electric potential of the analog video signal in the video signal correction circuit, a correc- 20 tion circuit for correcting the electric power source potential may also be added, similar to the digital drive EL display. Embodiment 2

A method of manufacturing an EL display which uses the present invention is explained using FIGS. 10A to 13B. A 25 method of manufacturing a TFT of a sensor portion is explained here, but it is also possible to similarly manufacture a TFT of a display portion.

First, as shown in FIG. 10A, a base film 501 is formed to a thickness of 300 nm on a glass substrate 500. A silicon 30 oxynitride film is laminated as the base film 501 in Embodiment 2. At this point, it is appropriate to set the nitrogen concentration to between 10 and 25 wt % in the film contacting the glass substrate 500. In addition, it is effective DLC (diamond-like carbon) film may also be provided.

Next, an amorphous silicon film (not shown in the figure) is formed with a thickness of 50 nm on the base film 501 by a known deposition method. Note that it is not necessary to limit to the amorphous silicon film, and another film may be 40 formed provided that it is a semiconductor film containing an amorphous structure (including a microcrystalline semiconductor film). In addition, a compound semiconductor film containing an amorphous structure, such as an amorphous silicon germanium film, may also be used. Further, the 45 film thickness may be made from 20 to 100 nm.

The amorphous silicon film is then crystallized by a known technique, forming a crystalline silicon film (also referred to as a polycrystalline silicon film or a polysilicon film) 502. Thermal crystallization using an electric furnace, 50 laser annealing crystallization using a laser light, and lamp annealing crystallization using an infrared lamp exist as known crystallization methods. Crystallization is performed in Embodiment 2 using an excimer laser light, which uses XeCl gas.

Note that pulse emission excimer laser light formed into a linear shape is used in Embodiment 2, but a rectangular shape may also be used. Continuous emission argon laser light and continuous emission excimer laser light can also be used

In this embodiment, although the crystalline silicon film is used as the active layer of the TFT, it is also possible to use an amorphous silicon film as the active layer.

Note that it is effective to form the active layer of the switching TFT, in which there is a necessity to reduce the off 65 current, by an amorphous silicon film, and to form the active layer of an EL driving TFT by a crystalline silicon film.

Electric current flows with difficulty in the amorphous silicon film because the carrier mobility is low, and the off current does not easily flow. In other words, the most can be made of the advantages of both the amorphous silicon film, through which current does not flow easily, and the crystalline silicon film, through which current easily flows.

Next, as shown in FIG. 10B, a protective film 503 is formed on the crystalline silicon film 502 with a silicon oxide film having a thickness of 130 nm. This thickness may be chosen within the range of 100 to 200 nm (preferably between 130 and 170 nm). Furthermore, other films may also be used providing that they are insulating films containing silicon. The protective film 503 is formed so that the crystalline silicon film is not directly exposed to plasma during addition of an impurity, and so that it is possible to have delicate concentration control of the impurity.

Resist masks 504a and 504b are then formed on the protective film 503, and an impurity element, which imparts n-type conductivity (hereafter referred to as an n-type impurity element), is added through the protective film 503. Note that elements residing in periodic table group 15 are generally used as the n-type impurity element, and typically phosphorous or arsenic can be used. Note that a plasma doping method is used, in which phosphine (PH<sub>3</sub>) is plasmaactivated without separation of mass, and phosphorous is added at a concentration of 1×10<sup>18</sup> atoms/cm<sup>3</sup> in Embodiment 2. An ion implantation method, in which separation of mass is performed, may also be used, of course.

The dose amount is regulated such that the n-type impurity element is contained in an n-type impurity region (b) 505, thus formed by this process, at a concentration of  $2\times10^{16}$  to  $5\times10^{19}$  atoms/cm<sup>3</sup> (typically between  $5\times10^{17}$  and  $5\times10^{18}$  atoms/cm<sup>3</sup>).

Next, as shown in FIG. 10C, the protective film 503 and that the base film 501 has a thermal radiation effect, and a 35 the resist masks 504a and 504b are removed, and an activation of the added n-type impurity elements is performed. A known technique of activation may be used as the means of activation, but activation is done in Embodiment 2 by irradiation of excimer laser light (laser annealing). Of course, a pulse emission excimer laser and a continuous emission excimer laser may both, be used, and it is not necessary to place any limits on the use of excimer laser light. The goal is the activation of the added impurity element, and it is preferable that irradiation is performed at an energy level at which the crystalline silicon film does not melt. Note that the laser irradiation may also be performed with the protective film 503 in place.

> The activation by heat treatment (furnace annealing) may also be performed along with activation of the impurity element by laser light. When activation is performed by heat treatment, considering the heat resistance of the substrate, it is good to perform heat treatment at on the order of 450 to 550° C.

A boundary portion (connecting portion) with end por-55 tions of the n-type impurity region (b) 505, namely regions, in which the n-type impurity element is not added, on the periphery of the n-type impurity region (b) 505, is delineated by this process. This means that, at the point when the TFTs are later completed, extremely good connecting portion can 60 be formed between LDD regions and channel forming

Unnecessary portions of the crystalline silicon film are removed next, as shown in FIG. 10D, and island-shape semiconductor films (hereafter referred to as active layers) **506** to **509** are formed.

Then, as shown in FIG. 10E, a gate insulating film 510 is formed, covering the active layers 506 to 509. An insulating

film containing silicon and with a thickness of 10 to 200 nm, preferably between 50 and 150 nm, may be used as the gate insulating film **510**. A single layer structure or a lamination structure may be used. A 110 nm thick silicon oxynitride film is used in Embodiment 2.

Thereafter, a conductive film having a thickness of 200 to 400 nm is formed and patterned to form gate electrodes 511 to 515. In Embodiment 2, the gate electrodes and wirings (hereinafter referred to as gate wirings) electrically connected to the gate electrodes for providing conductive paths are formed of different materials from each other. More specifically, the gate wirings are made of a material having a lower resistivity than the gate electrodes. This is because a material enabling fine processing is used for the gate electrodes, while the gate wirings are formed of a material that can provide a smaller wiring resistance but is not suitable for fine processing. It is of course possible to form the gate electrodes and the gate wirings with the same material.

Although the gate electrode can be made of a single-layered conductive film, it is preferable to form a lamination 20 film with more than two layers for the gate electrode if necessary. Any known conductive films can be used for the gate electrode. It should be noted, that it is preferable to use such a material that enables fine processing, and more specifically, a material that can be patterned with a line 25 width of 2  $\mu$ m or less.

Typically, it is possible to use a film made of an element selected from the group consisting of tantalum (Ta), titanium (Ti), molybdenum (Mo), tungsten (W), chromium (Cr), and silicon (Si), a film of nitride of the above element (typically 30 a tantalum nitride film, tungsten nitride film, or titanium nitride film), an alloy film of combination of the above elements (typically Mo-W alloy or Mo-Ta alloy), or a silicide film of the above element (typically a tungsten silicide film or titanium silicide film). Of course, the films 35 may be used as a single layer or a laminate layer.

In Embodiment 2, a laminate film of a tungsten nitride (WN) film having a thickness of 30 nm and a tungsten (W) film having a thickness of 370 nm is used. This may be formed by sputtering. When an inert gas such as Xe or Ne 40 is added as a sputtering gas, film peeling due to stress can be prevented.

The gate electrode **511** is formed at this time so as to overlap a portion of the n-type impurity region (b) **505**. This overlapping portion later becomes an LDD region overlapping the gate electrode (FIG. **10E**).

Next, an n-type impurity element (phosphorous is used in Embodiment 2) is added in a self-aligning manner with the gate electrodes **511** to **515** as masks, as shown in FIG. **11A**. The addition is regulated such that phosphorous is added to 50 n-type impurity regions (c) **516** to **523** thus formed at a concentration of  $\frac{1}{10}$  to  $\frac{1}{2}$  that of the n-type impurity region (b) **505** (typically between  $\frac{1}{4}$  and  $\frac{1}{3}$ ). Specifically, a concentration of  $1\times10^{16}$  to  $5\times10^{18}$  atoms/cm<sup>3</sup> (typically  $3\times10^{17}$  to  $3\times10^{18}$  atoms/cm<sup>3</sup>) is preferable.

Resist masks 524a to 524c are formed next, with a shape covering the gate electrodes 512 to 515 and the like, as shown in FIG. 11B, and an n-type impurity element (phosphorous is used in Embodiment 2) is added, forming impurity regions (a) 525 to 529 containing phosphorous at 60 high concentration. Ion doping using phosphine (PH<sub>3</sub>) is also performed here, and the phosphorous concentration of these regions is regulated so as to be set to from  $1\times10^{20}$  to  $1\times10^{21}$  atoms/cm<sup>3</sup> (typically between  $2\times10^{20}$  and  $5\times10^{20}$  atoms/cm<sup>3</sup>).

A source region or a drain region of the n-channel TFT is formed by this process, and in a switching TFT, a portion of the n-type impurity regions (c) 519 to 521 formed by the process of FIG. 11A is remained. These remaining regions correspond to LDD regions of the switching TFT.

Next, as shown in FIG. 11C, the resist masks 524a to 524d are removed, and new resist masks 530a and 530b are formed. A p-type impurity element (boron is used in Embodiment 2) is then added, forming p-type impurity regions 531 to 534 containing boron at high concentration. Boron is added here to form the p-type impurity regions 531 to 534 at a concentration of  $3\times10^{20}$  to  $3\times10^{21}$  atoms/cm<sup>3</sup> (typically between  $5\times10^{20}$  and  $1\times10^{21}$  atoms/cm<sup>3</sup>) by ion doping using diborane (B<sub>2</sub>H<sub>6</sub>).

Note that phosphorous has already been added to the p-type impurity regions 531 to 534 at a concentration of  $1\times10^{20}$  to  $1\times10^{21}$  atoms/cm<sup>3</sup>, but boron is added here at a concentration of at least 3 times that of the phosphorous. Therefore, the n-type impurity regions already formed completely invert to p-type, and function as p-type impurity regions.

Next, after removing the resist masks **530***a* and **530***b*, the n-type or p-type impurity elements added to the active layer at respective concentrations are activated. Furnace annealing, laser annealing or lamp annealing can be used as a means of activation. In Embodiment 2, heat treatment is performed for 4 hours at 550° C. in a nitrogen atmosphere in an electric furnace.

At this time, it is critical to eliminate oxygen from the surrounding atmosphere as much as possible. This is because when even only a small amount of oxygen exists, an exposed surface of the gate electrode is oxidized, which results in an increased resistance and later makes it difficult to form an ohmic contact with the gate electrode. Accordingly, the oxygen concentration in the surrounding atmosphere for the activation process is set at 1 ppm or less, preferably at 0.1 ppm or less.

After the activation process is completed, a gate wiring (gate signal line) 535 having a thickness of 300 nm is formed. As a material for the gate wiring 535, a metal film containing aluminum (Al) or copper (Cu) as its main component (occupied 50 to 100% in the composition) can be used. The gate wiring 335 is arranged so as to provide electrical connection for the gate electrodes 513 and 514 of the switching TFT (see FIG. 11D).

The above-described structure can allow the wiring resistance of the gate wiring to be significantly reduced, and therefore, an image display region (display portion) with a large area can be formed. More specifically, the pixel structure in accordance with Embodiment 2 is advantageous for realizing an EL display device having a display screen with a diagonal size of 10 inches or larger (or 30 inches or larger.)

A first interlayer insulating film 537 is formed next, as shown in FIG. 12A. A single layer insulating film containing silicon is used as the first interlayer insulating film 537, or a lamination film may be used. Further, a film thickness of between 400 nm and 1.5  $\mu$ m may be used. A lamination structure of an 800 nm thick silicon oxide film on a 200 nm thick silicon oxynitride film is used in Embodiment 2.

In addition, heat treatment is performed for 1 to 12 hours at 300 to 450° C. in an atmosphere containing between 3 and 100% hydrogen, performing hydrogenation. This process is one of hydrogen termination of dangling bonds in the semiconductor film by hydrogen, which is thermally activated. Plasma hydrogenation (using hydrogen activated by plasma) may also be performed as another means of hydrogenation.

Note that the hydrogenation processing may also be inserted during the formation of the first interlayer insulating

film 537. Namely, hydrogen processing may be performed as above after forming the 200 nm thick silicon oxynitride film, and then the remaining 800 nm thick silicon oxide film may be formed.

Next, a contact hole is formed in the first interlayer 5 insulating film 537, and source wirings 538 to 541 and drain wirings 542 to 545 are formed. In this embodiment, this electrode is made of a laminate film of three-layer structure in which a titanium film having a thickness of 100 nm, an aluminum film containing titanium and having a thickness of 10 556 may be formed by patterning an acrylic film or poly-300 nm, and a titanium film having a thickness of 150 nm are continuously formed by sputtering. Of course, other conductive films may be used.

A first passivation film 547 is formed next with a thickness of 50 to 500 nm (typically between 200 and 300 nm) as 15 shown in FIG. 12B. A 300 nm thick silicon oxide nitride film is used as the first passivation film 547 in Embodiment 2. This may also be substituted by a silicon nitride film. Note that it is effective to perform plasma processing using a gas containing hydrogen such as H<sub>2</sub> or NH<sub>3</sub> before the formation 20 of the silicon oxynitride film. Hydrogen activated by this preprocess is supplied to the first interlayer insulating film 537, and the film quality of the first passivation film 547 is improved by performing heat treatment. At the same time, the hydrogen added to the first interlayer insulating film 537 25 diffuses to the lower side, and the active layers can be hydrogenated effectively.

Next, a second interlayer insulating film 548 made of organic resin is formed. As the organic resin, it is possible to use polyimide, polyamide, acryl, BCB 30 (benzocyclobutene) or the like. Especially, since the second interlayer insulating film 548 is primarily used for leveling, acryl excellent in leveling properties is preferable. In this embodiment, an acrylic film is formed to a thickness sufficient to level a stepped portion formed by TFTs. It is 35 appropriate that the thickness is made 1 to 5  $\mu$ m (more preferably, 2 to 4  $\mu$ m) (FIG. 12B).

Next, a contact hole is formed in the second interlayer insulating film 548 and the first passivation film 547 so as to reach the drain wiring 543, and a cathode electrode 549 of 40 a light receiving diode (photoelectric converting element) is formed so as to contact the drain wiring 543. Aluminum formed by sputtering is used in this metallic film in Embodiment 2, but other metals, for example titanium, tantalum, tungsten, and copper can also be used. Further, a lamination 45 film made from titanium, aluminum, and titanium may also